Completed Projects

Completed: Researching novel and effective approaches for securing the Internet of Things (IoT) hardware against cutting edge Deep-learning-based Power Side-channel Attacks (DeePSAs) using emerging devices

- Developing EDA tool flows for secure hardware design using Machine Learning.

- Demonstrate innovative use of supervised and unsupervised deep learning approaches to develop the proposed Deep-learning-based Power Side-channel Attack (DeePSA), which can accurately estimate the encryption key from sampled power traces even in the presence of process variation, signal noise, and perturbation.

- Demonstrate utilization of commercially available STT-MRAM to design energy and area-optimized Look-Up Tables (LUTs) for the encryption hardware to mitigate the proposed DeePSA, called Secure Hardware for IoT using Emerging-devices against side-channeL Deep-learning attacks (SHIELD).

Completed: Researched beyond von Neumann computing architectures for Internet of Things (IoT) devices and ambient-powered intelligent edge processing

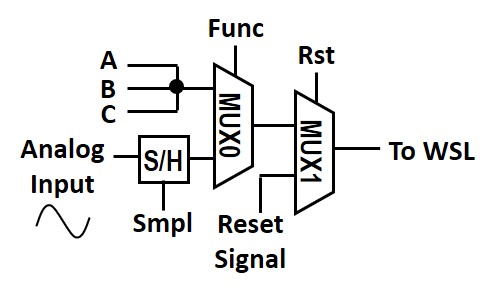

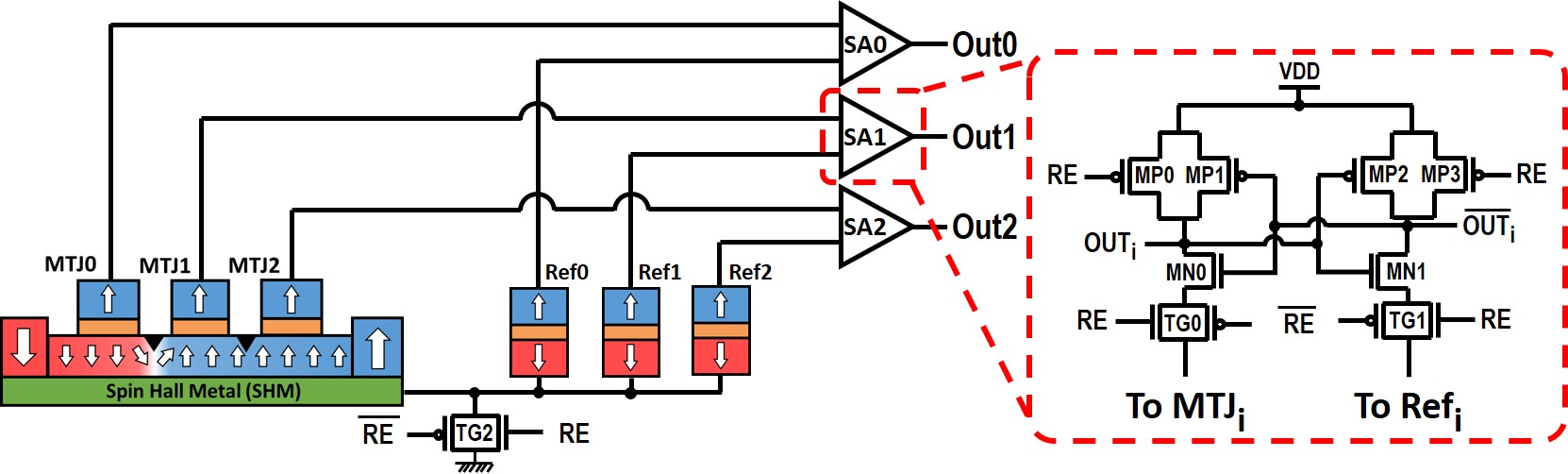

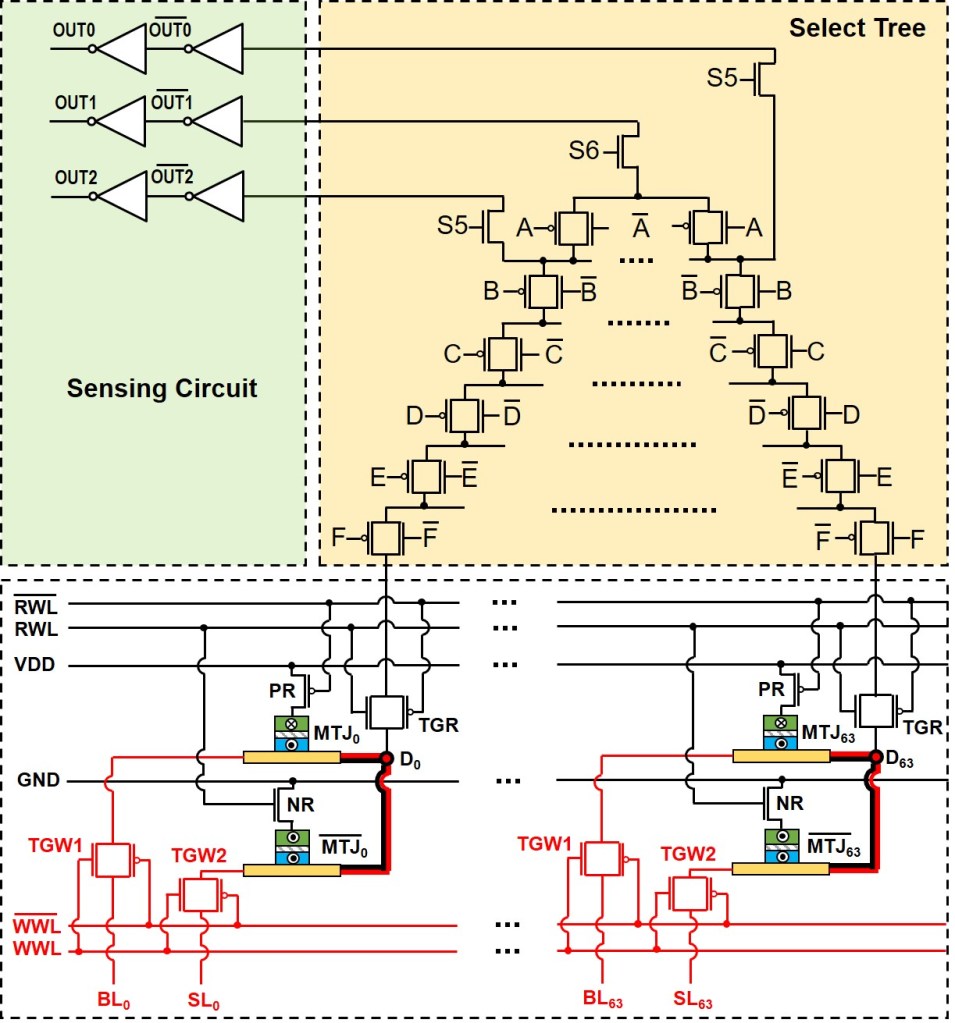

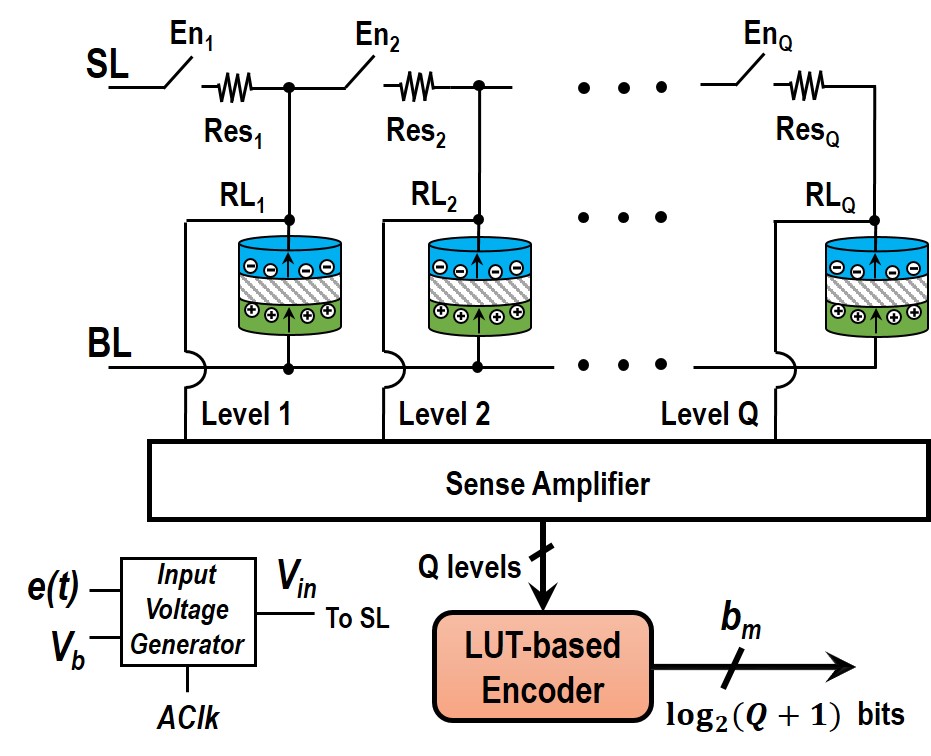

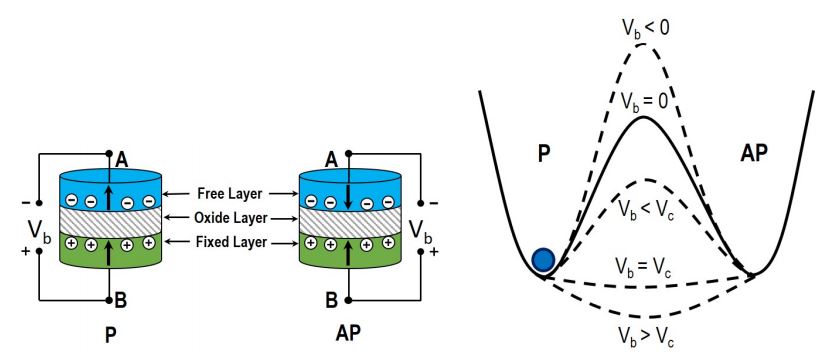

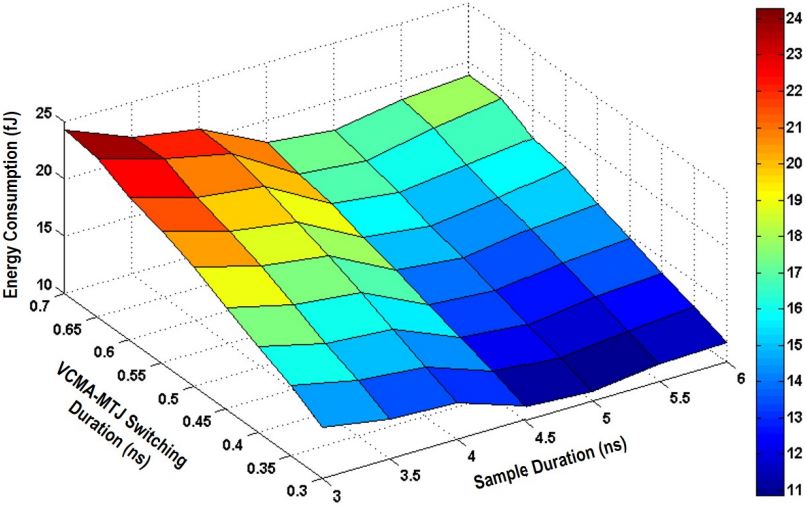

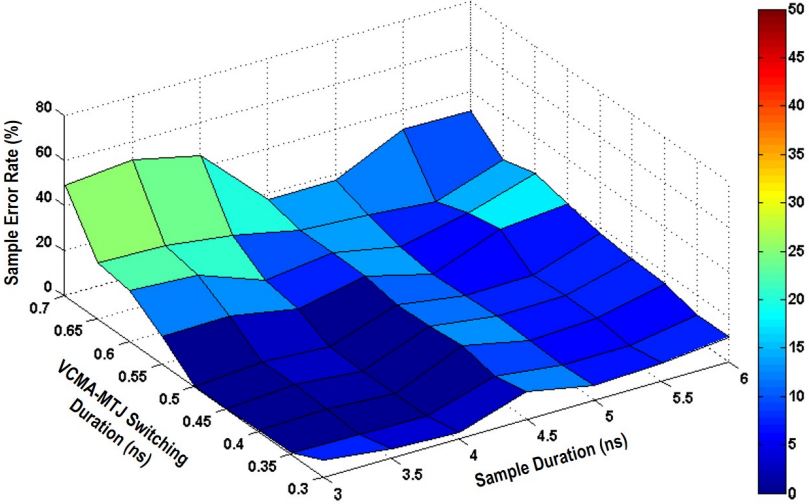

- Proposed a Spin-based Logic In Memory Analog to Digital Converter (SLIM-ADC) that provides a compact ADC to perform energy-efficient signal conversion and logical operations. SLIM-ADC offers 200fJ energy consumption on average for each ADC or logic operation with up to 1GHz speed. SLIM-ADC outperforms other state-of-the-art spin-based ADCs by offering 5.45mW improved power dissipation on average. A Majority-Gate-based Full-Adder implemented using SLIM-ADC offers 2.9-fold reduced power dissipation on average and 1.7-fold reduced delay on average compared to the state-of-the-art spin-based Full-Adder designs.

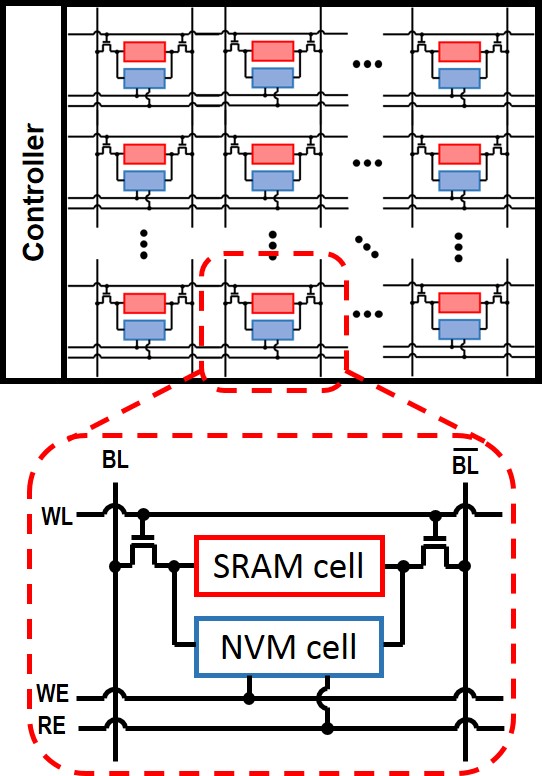

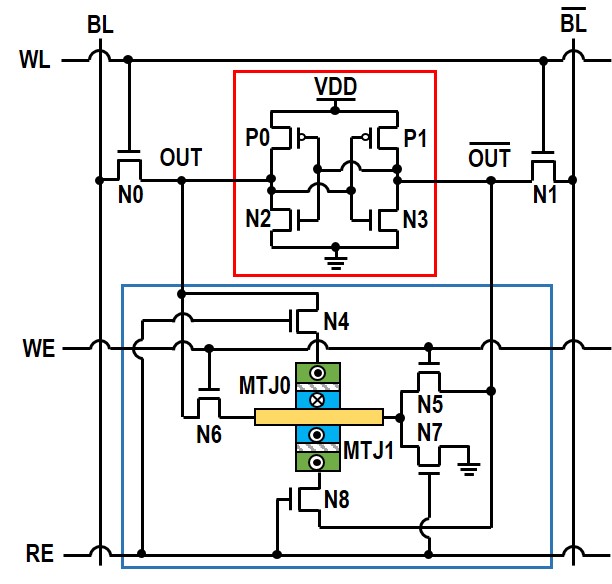

- Proposed a Bit-Grained Instant-on Memory Cell (BGIM) that is an energy-aware Non-Volatile Static Random Access Memory framework for sleep power critical mobile applications. BGIM consumes 121.51fJ on average for each backup operation and 1.56fJ on average for each restore operation. BGIM can perform rapid backup operations in 1ns and fast restore operations in 13.2ps. BGIM cell incurs 0.4um^2 area overhead compared to the traditional 6T SRAM cell, however it eliminates the need for data transmission and a separate non-volatile memory macro.

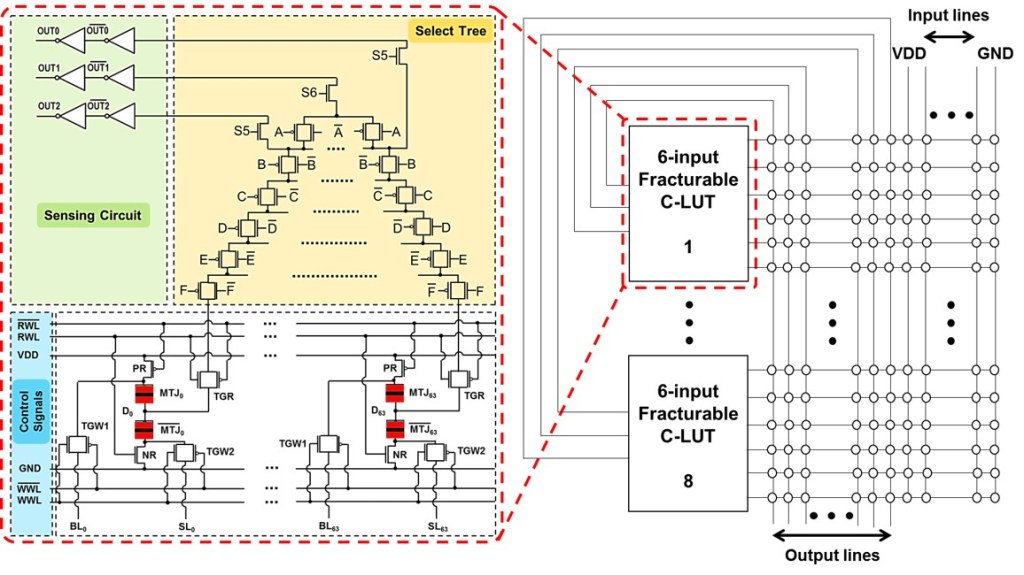

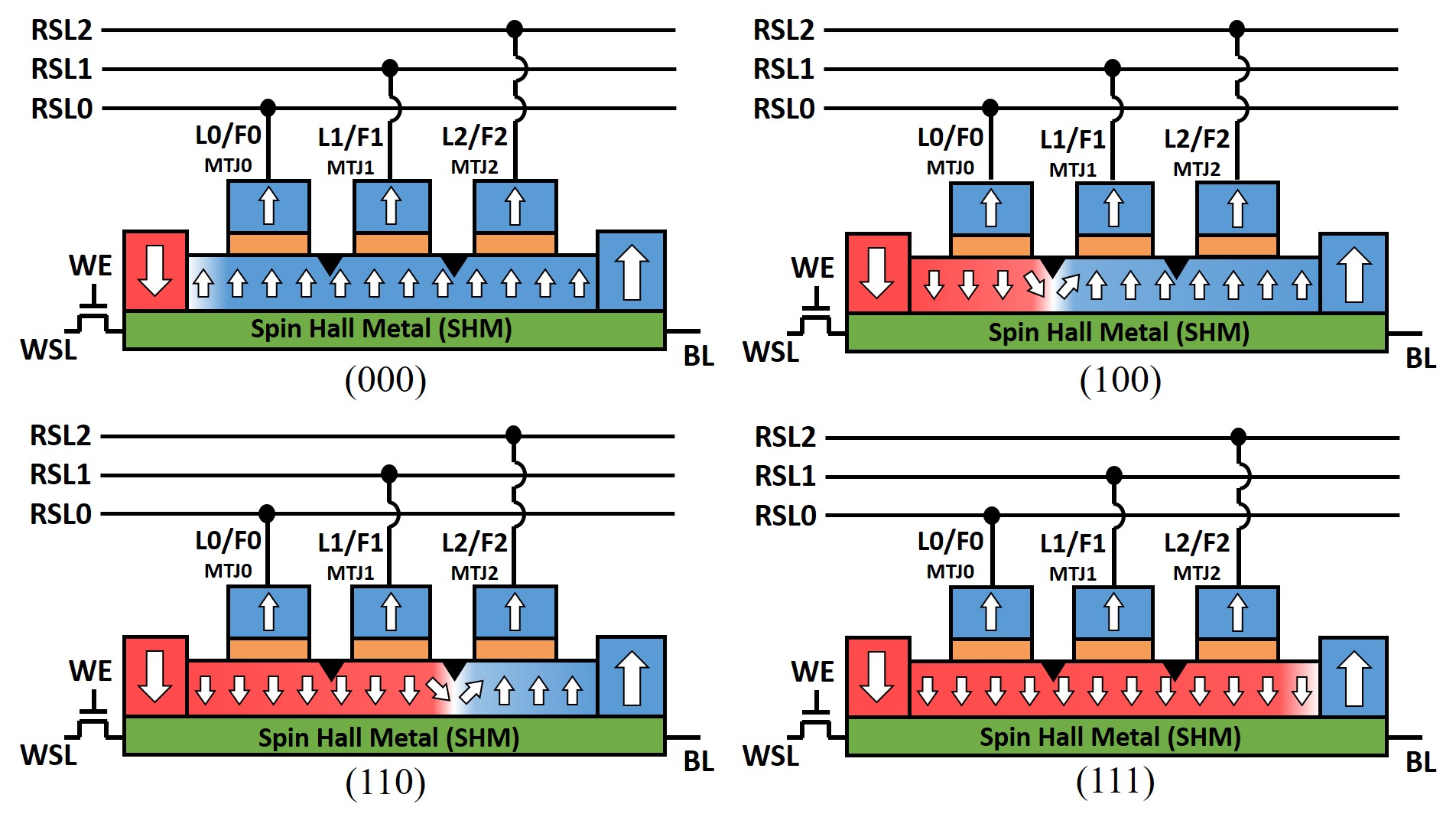

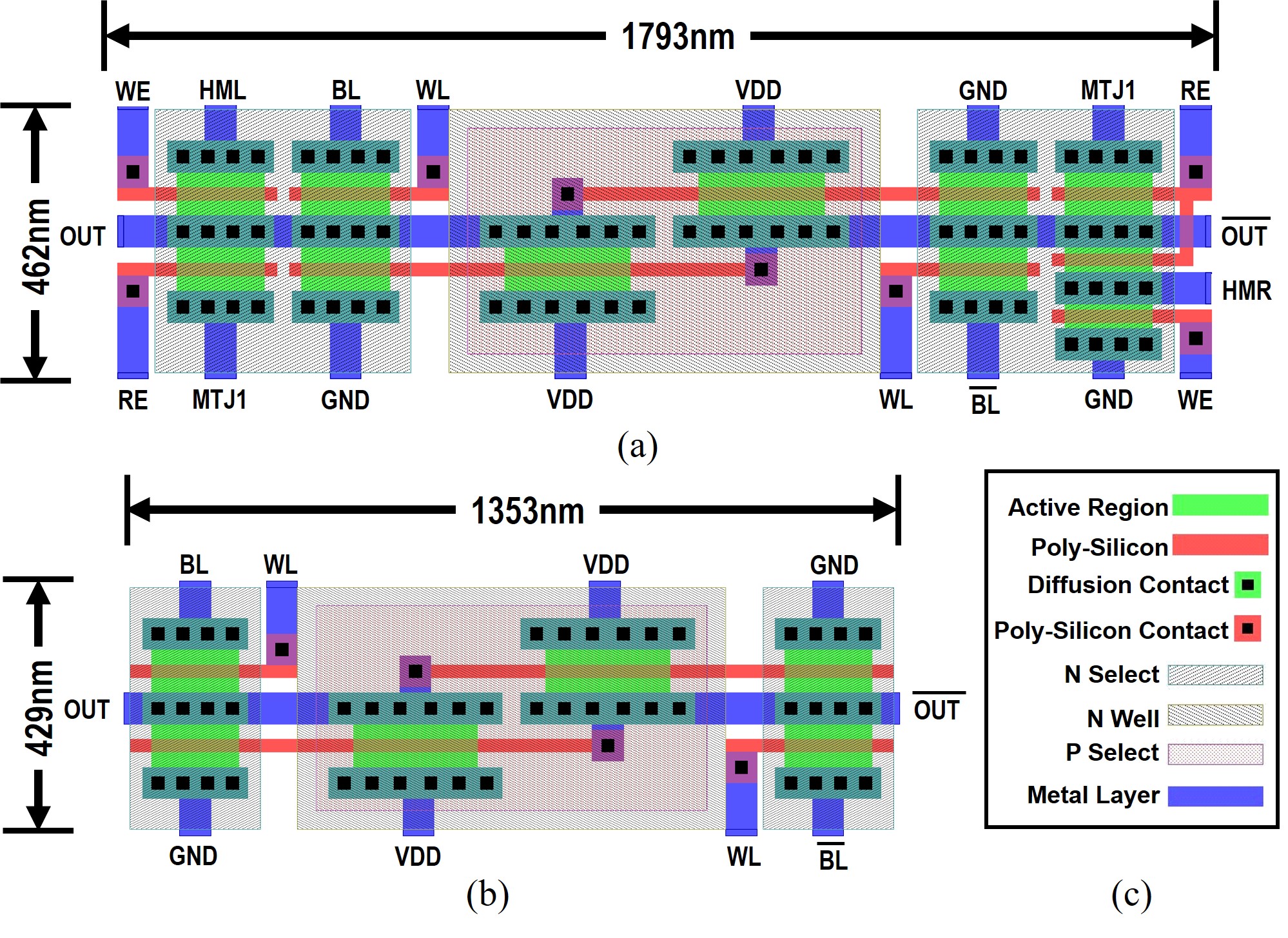

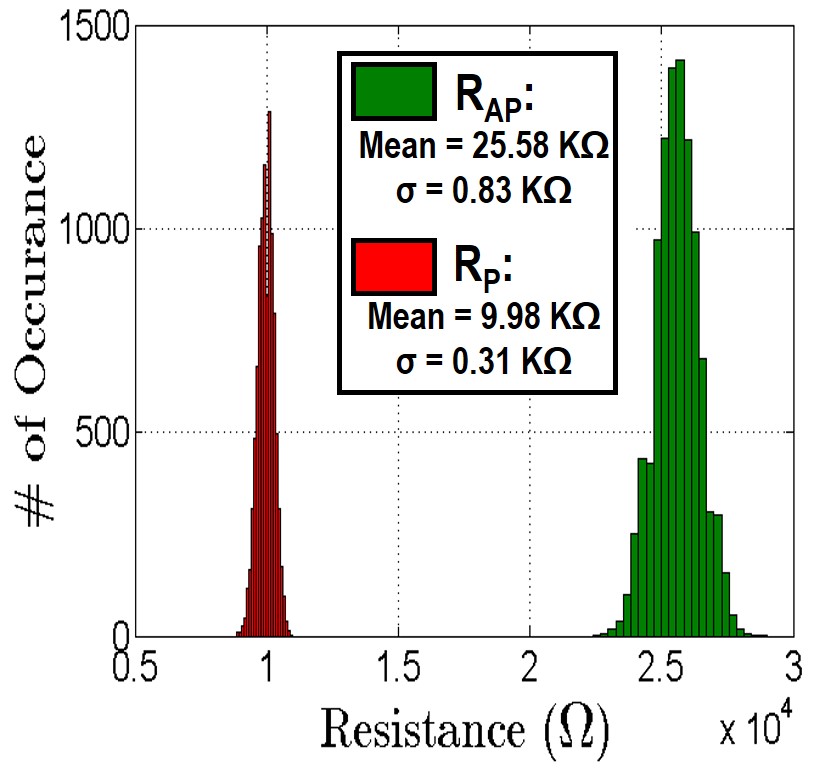

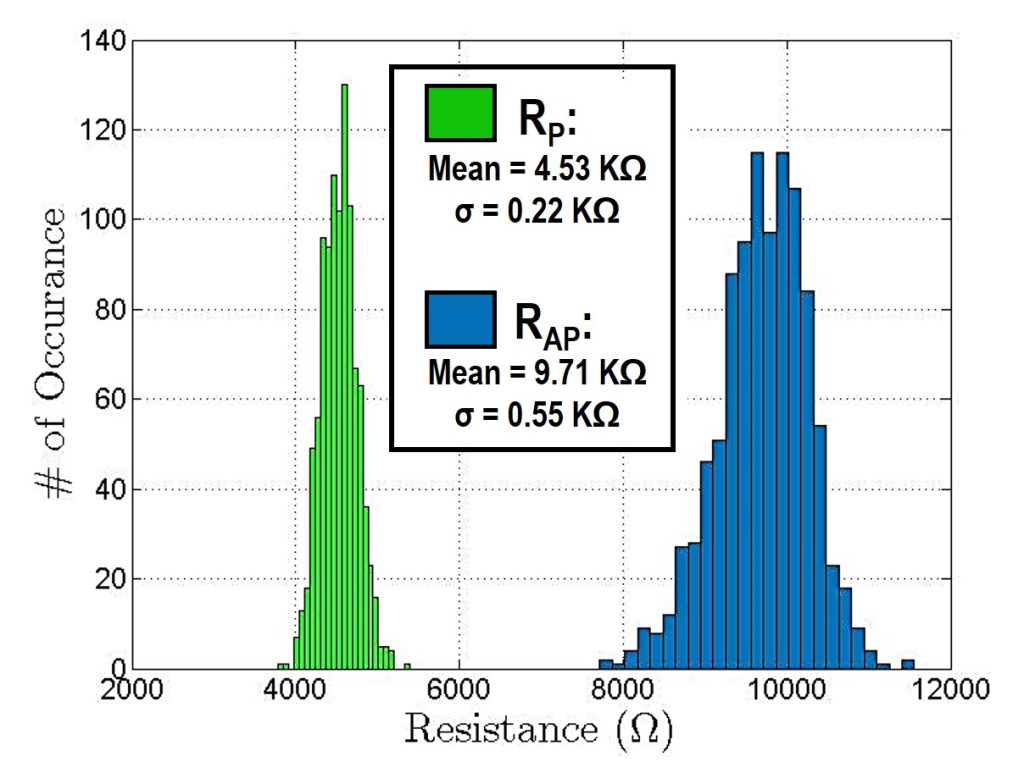

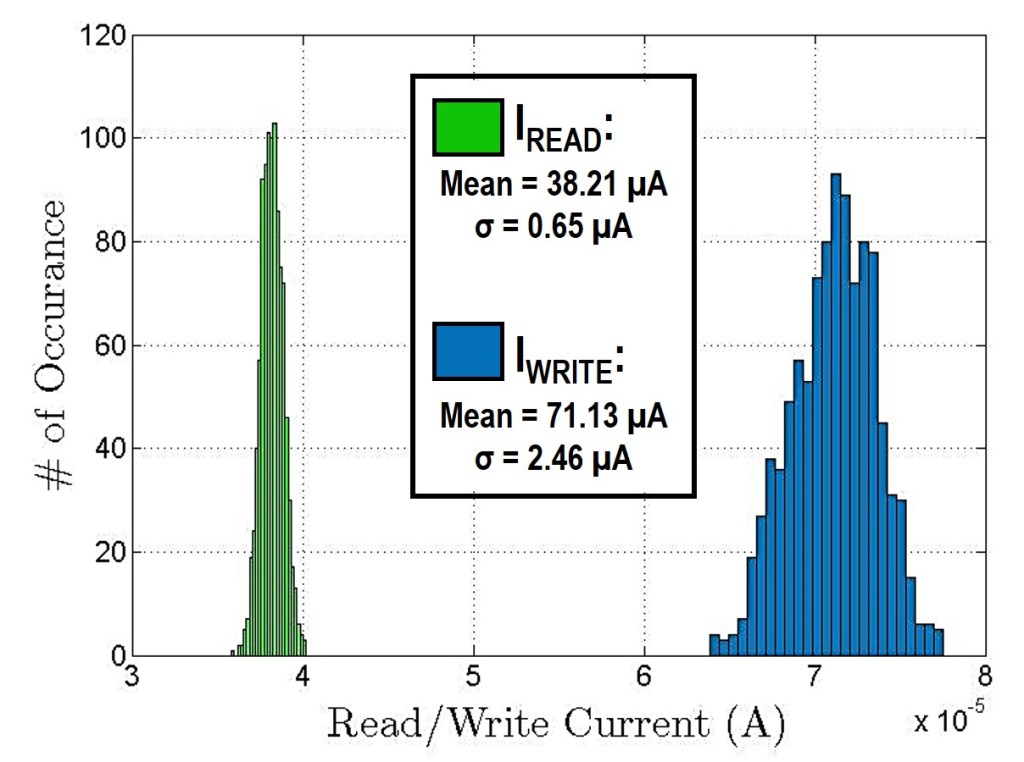

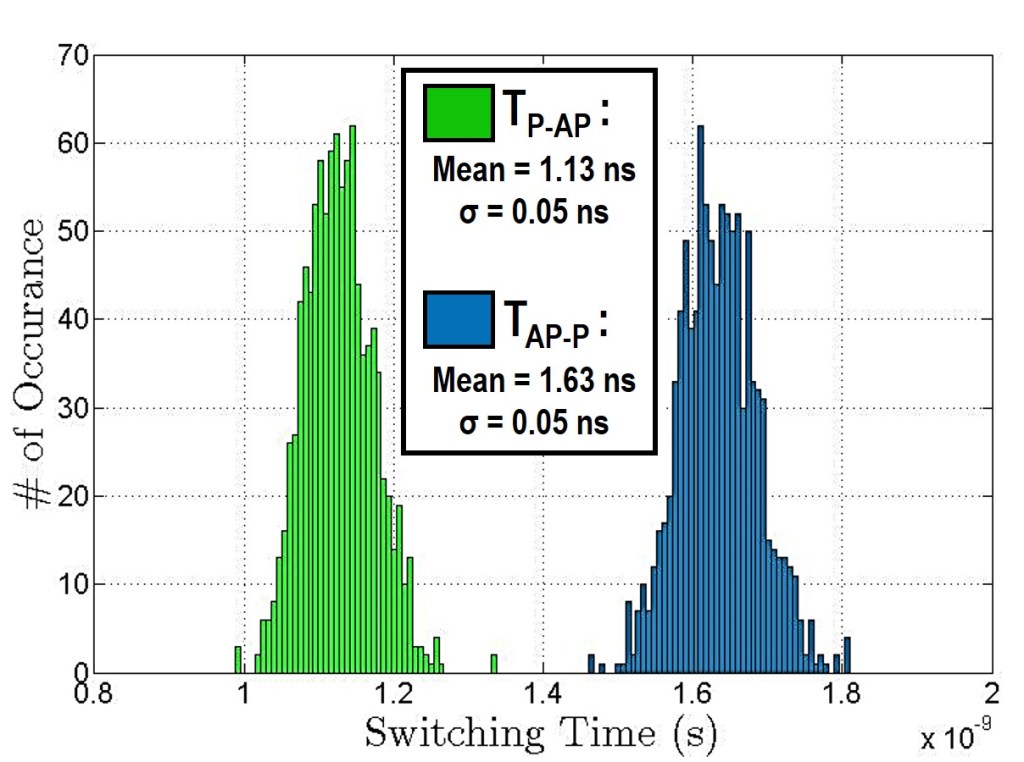

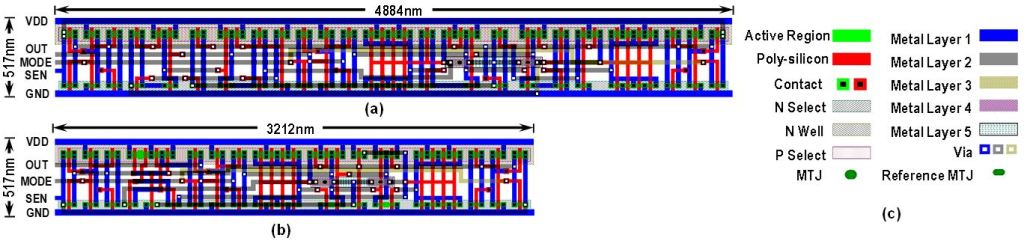

- Proposed a 6-input fracturable non-volatile Clockless LUT (C-LUT) that can implement combinational logic as well as sequential logic while eliminating the sense amplifier to realize much wider read margin. Monte Carlo simulation of the proposed fracturable C-LUT indicates no read and write errors in the presence of a variety of process variations scenarios involving MOS transistors as well as MTJs. C-LUT reduces the standby power dissipation by 5.4-fold compared to the SRAM-based LUT. Furthermore, the proposed SHE-MTJ-based C-LUT reduces the area by 1.3-fold and 2-fold compared to the SRAM-based LUT and the STT-MTJ-based C-LUT, respectively.

Completed: Designed circuits for energy-efficient and reliable memory and signal conversion applications leveraging 2-terminal commercially-available STT-MTJs and 3-terminal emerging SOT-MTJs

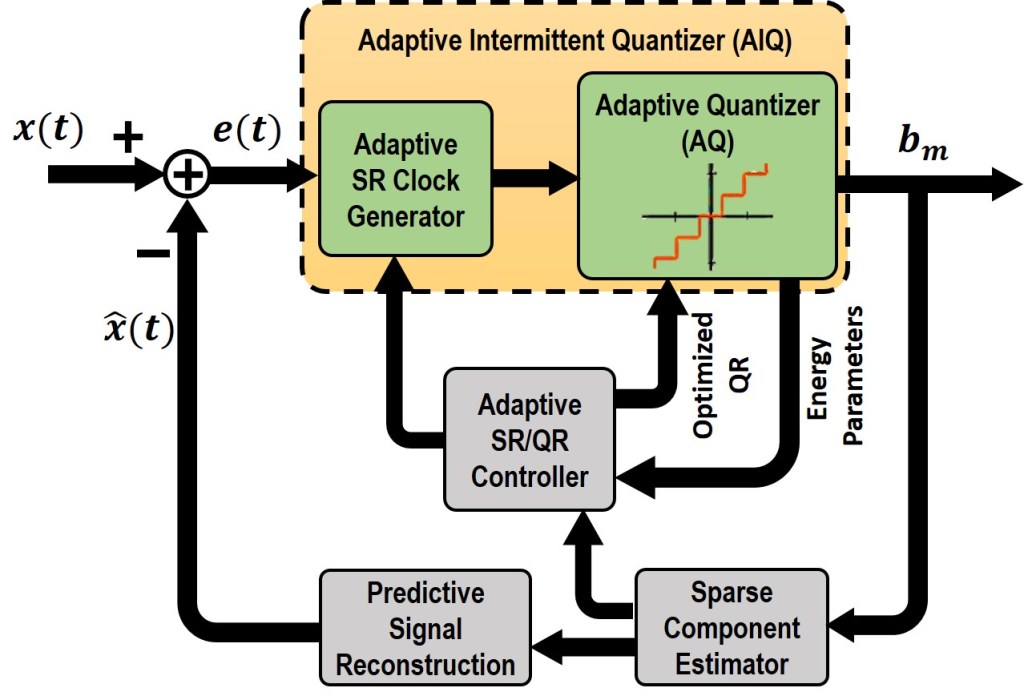

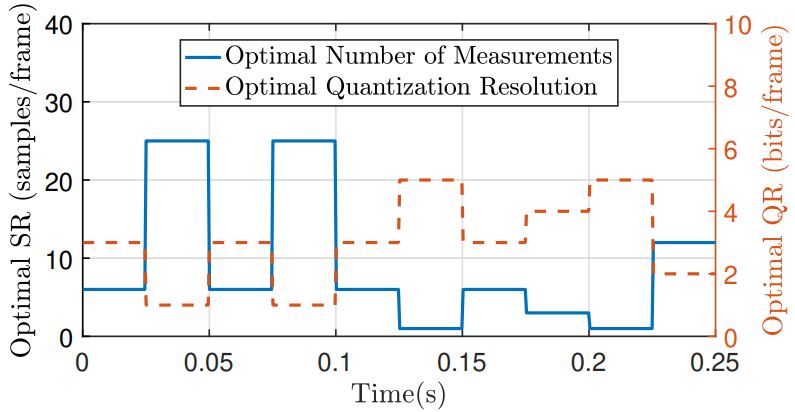

- Proposed a spin-based Adaptive Intermittent Quantizer (AIQ) to realize smart and adaptive determination of the sampling rate and quantization resolution based on the signal and hardware constraints. AIQ incurs only 20.98uW power dissipation on average for 1-8 bits uniform output, and provides maximum power dissipation of 85.302uW. AIQ provides up to 6.18mW power savings on average compared to other adaptive rate and resolution CMOS-based CS ADCs.

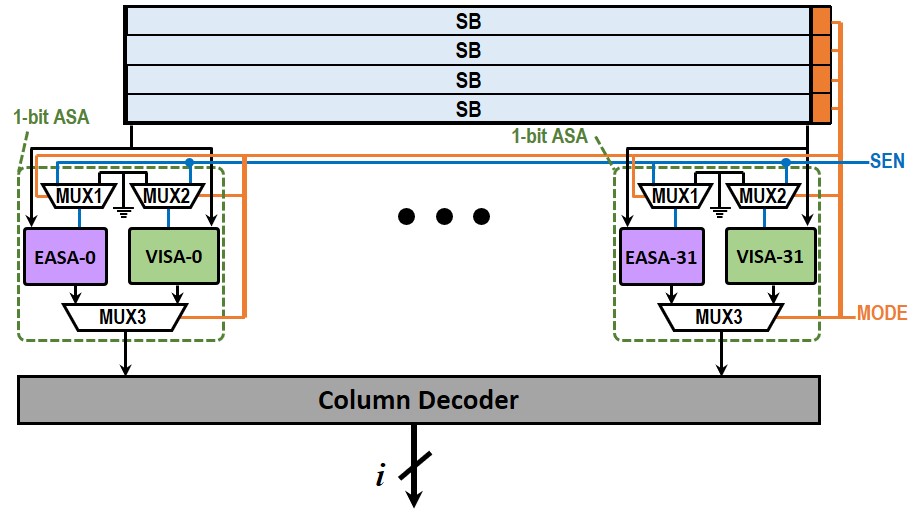

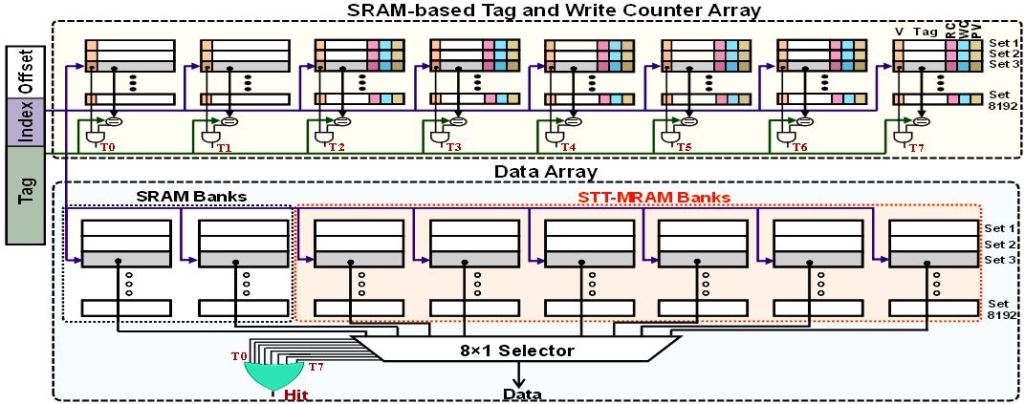

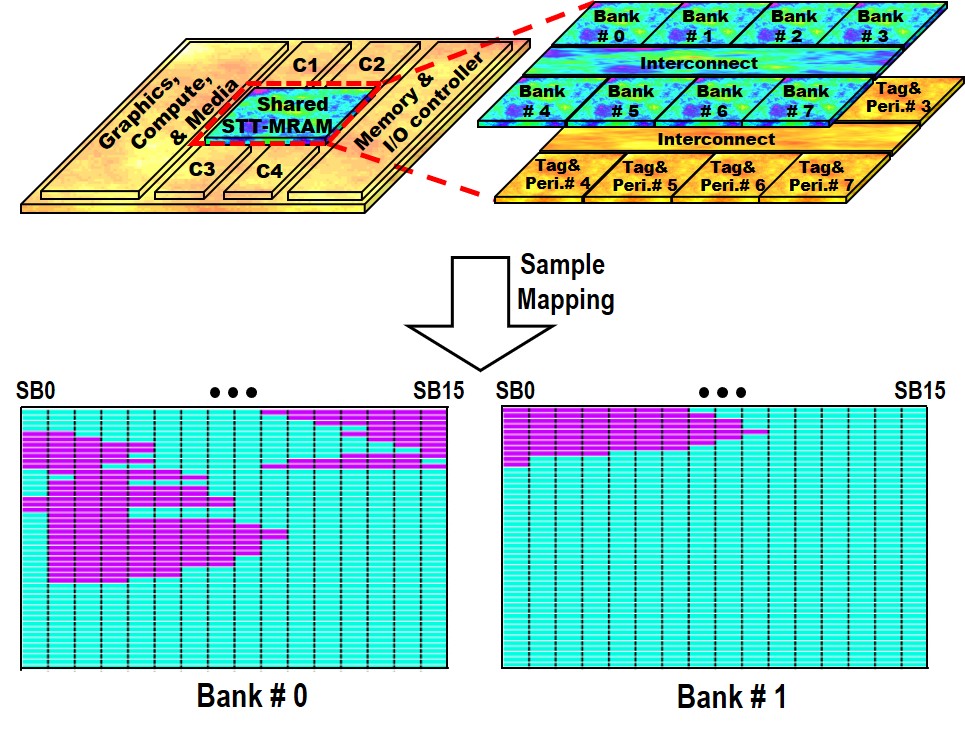

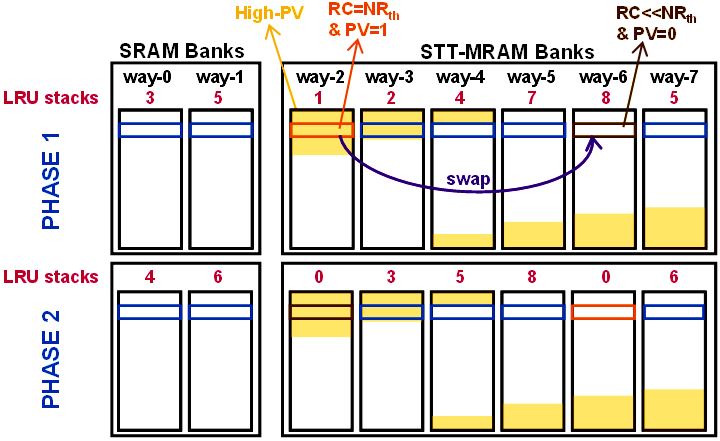

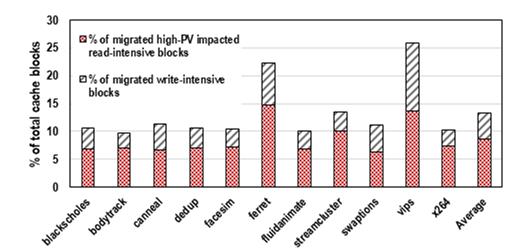

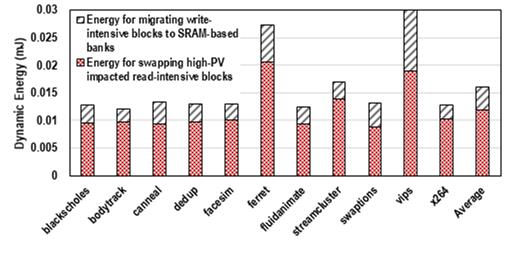

- Proposed a Self-Organized Sub-bank (SOS) design that assigns the preferred SA to each sub-bank based on a PV assessment, resulting in energy consumption reduction and increased read access reliability. Additionally, proposed a dynamic PV and energy-aware cache block migration policy utilizing hybrid SRAM/STT-MRAM banks in Last Level Cache. SOS can alleviate the sensing vulnerability by 89% on average, which significantly reduces the risk of application contamination by fault propagation. Proposed block migration policy improves write performance by 12.4% on average compared to the STT-MRAM-only design.

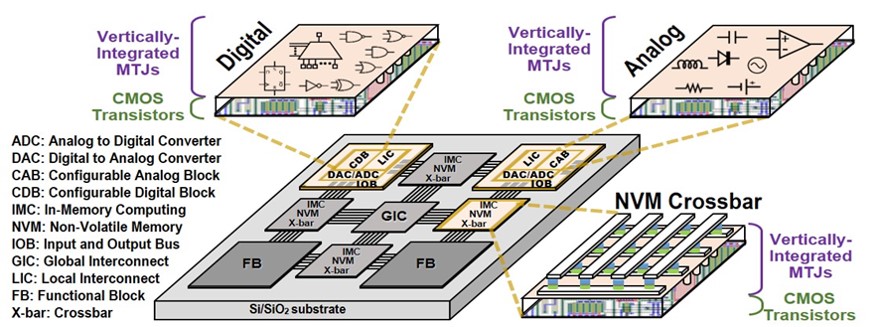

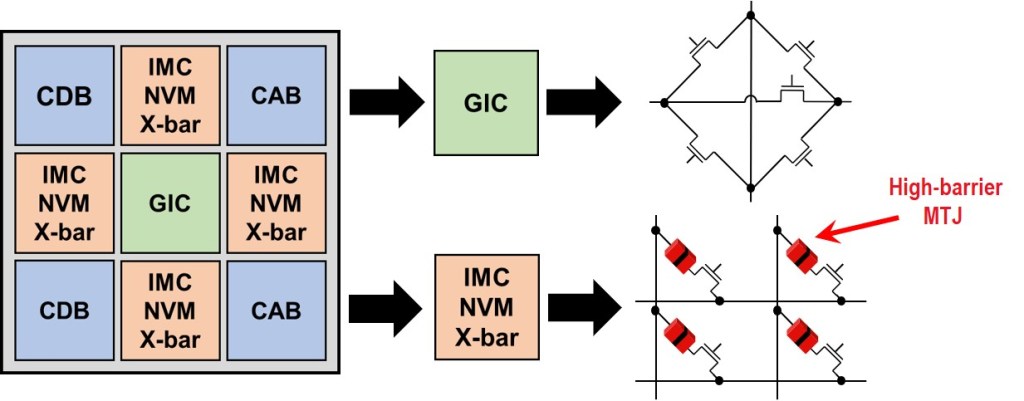

Completed: Developed mixed-signal cross-layer algorithmic and hardware approaches for heterogeneous technology reconfigurable computing fabrics for in-situ signal processing

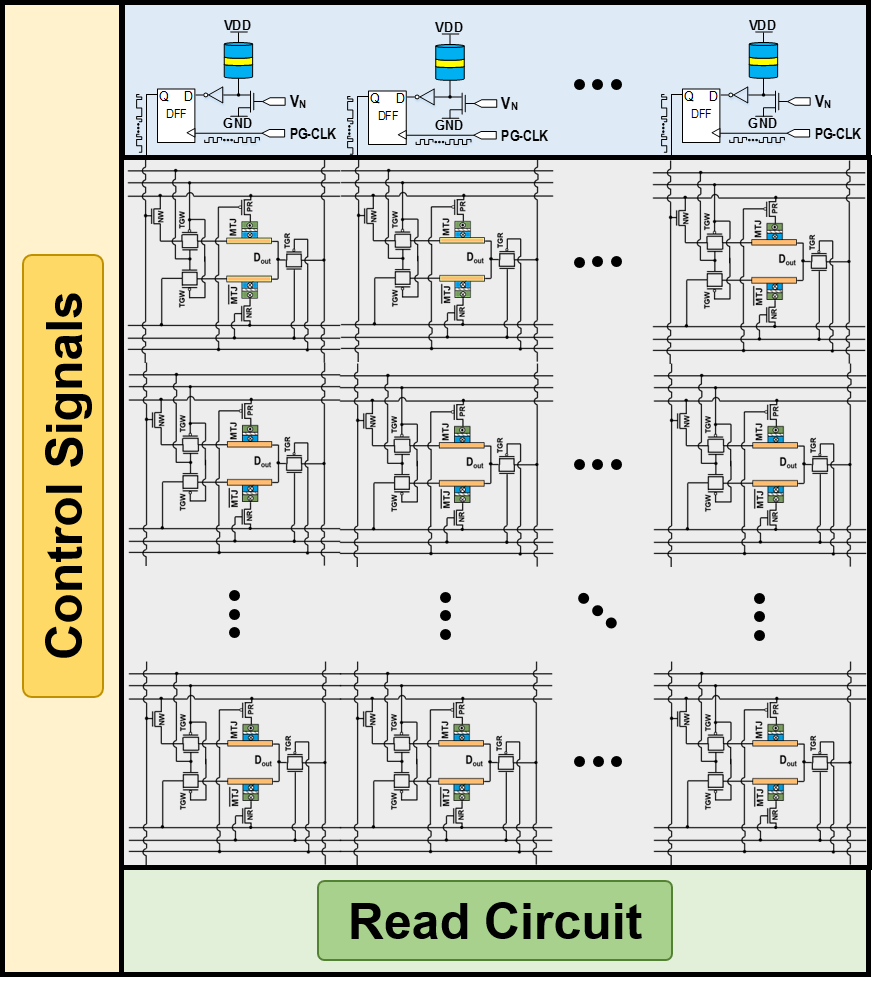

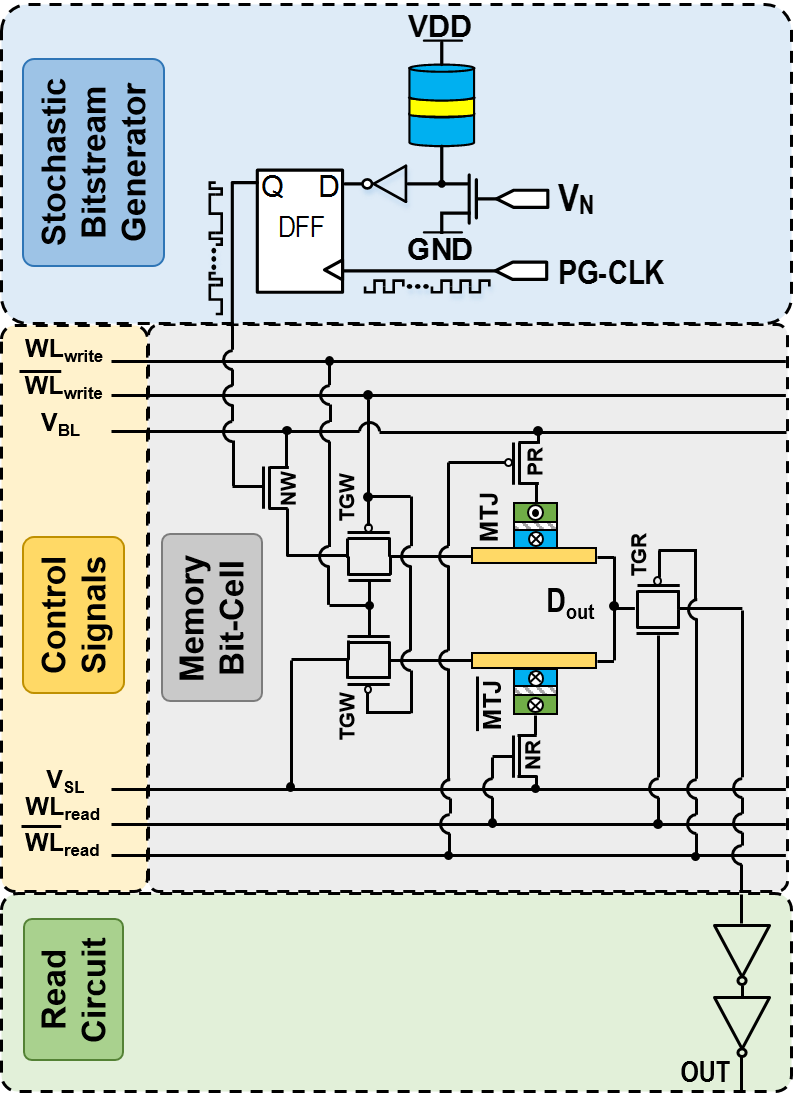

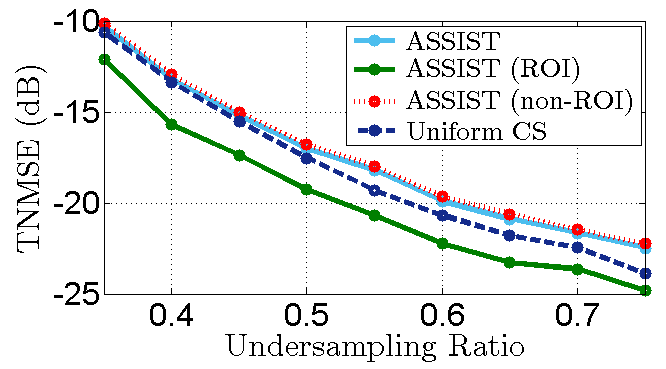

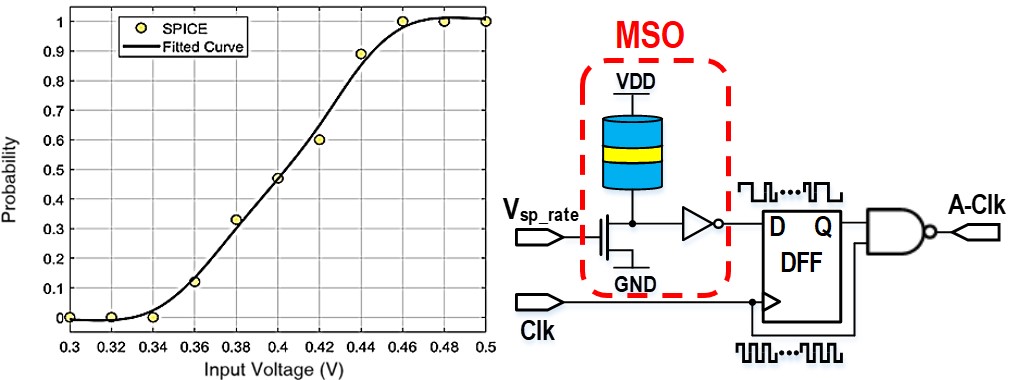

- Proposed an Adaptive Sampling of Sparse IoT signals via STochastic oscillators (ASSIST) which efficiently achieves the desired non-uniform recovery of the original signals with varying sparsity rates and noise levels. Additionally, MRAM-based Stochastic Oscillator (MSO) used as a TRNG provides significant area improvement of 3-fold while achieving energy consumption per bit reduction of 9-fold, on average, compared to similar TRNGs presented in the literature.

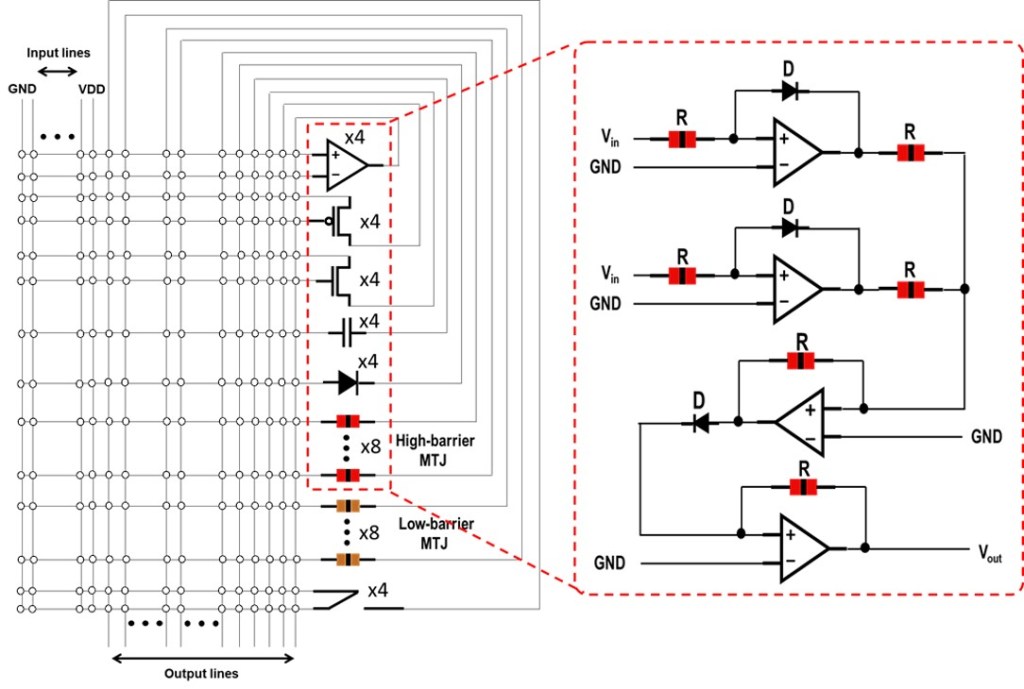

- Proposed a Mixed-signal Field Programmable Analog Array (M-FPAA) that provides a palette of analog and digital functional blocks to realize adaptive sampling and quantization rate based compressive sensing algorithms within a compact and reduced-energy reconfigurable fabric. M-FPAA functional blocks are connectable via programmable interconnect to a non-volatile crossbar to perform vector-matrix multiplication with 5-fold reduction in energy consumption and a 26-fold decrease in area requirement compared to CMOS-only approaches.